Cada día salen a la luz algunas nuevas informaciones sobre los nuevos procesadores destinados a servidores y la gama alta de sobremesa y estaciones de trabajo, los nuevos Bulldozer.

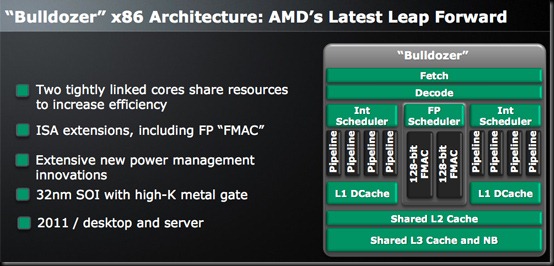

Como sabréis, Bulldozer supone un cambio importante para AMD y en general para el mundo X86, una verdadera revolución en el diseño dado que se comparten entre cores algunas estructuras de procesamiento, en este caso la unidad FPU y el FP scheduler.

Un módulo Bulldozer consta de dos cores de enteros.

Un módulo Bulldozer consta de dos cores de enteros.

Bulldozer module:

Cada módulo de Bulldozer se compone de dos cores de enteros con sus:

- Schedulers de enteros

- ALUs

- AGUs

- Caché L1d

En cambio la FPU es compartida por cada dos cores de enteros junto con su propio scheduler. También parece que la caché L1i (instrucciones) será compartida entre los dos cores dentro de cada módulo.

La FPU tiene capacidad de 256 bit por ciclo o 2 operaciones de 128 bit por ciclo, estas dos operaciones de 128 bit pueden ser de dos threads diferentes (ejecutados cada uno por uno de los INT cores del módulo) o de un solo thread ejecutado por uno de los INT cores.

Las cachés L2 son unificadas (datos e instrucciones) y son compartidas cada dos INT cores y la FPU (una L2 por módulo). No creo que sean de gran tamaño, sería más beneficiosa una muy baja latencia sobre los 10 ciclos y sobre 512 KB o 1 MB. Aunque siguiendo la tradición de AMD es probable que se decanten por un diseño de 2 MB y alta latencia (rondando los 15 ciclos).

Como pegas a un tamaño tan grande (2 MB) veo la dificultad en compaginarlo con una arquitectura de caché exclusiva con la L3, que forzaría un tamaño de L3 mayor de 8 MB.

La caché L3 es compartida por todo el procesador y su tamaño debe de ser importante, veo lógico como mínimo 8 MB en el proceso de 32 nm y 8 INT cores, aunque lo deseable serían unos 12 MB y lo óptimo 16 (2 MB por INT core).

Claro es que con tamaños de caché tan elevados, se iría la superficie de die a terrenos peligrosos en lo económico y también para conseguir buenos yields de fabricación.

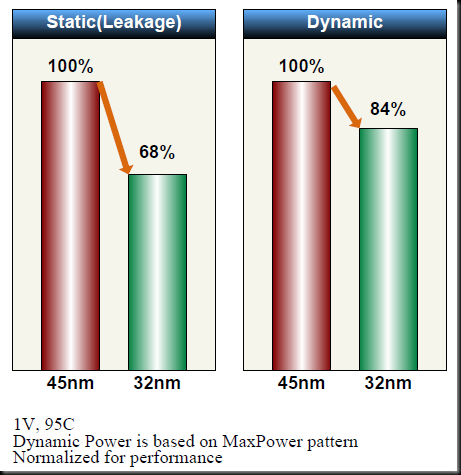

Una notable reducción del consumo en 32 nm permitirá a AMD modos Turbo más agresivos.

Una notable reducción del consumo en 32 nm permitirá a AMD modos Turbo más agresivos.

Según las ideas actuales AMD integrará en Bulldozer modos Turbo mucho más agresivos para acelerar las prestaciones single thread. Con este dato en mente es posible que logre superar a los cores Phenom II de 32 nm que aparecerán la APU Llano en 2011 en este aspecto IPC por core

AMD en 2011, Bulldozer para el mercado de sobremesa:

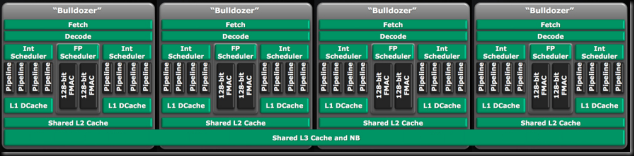

AMD lanzará dos versiones para sobremesa de Bulldozer, un quad core y un octal core, ambos contarán con dos controladoras DDR3 de 64 bit y hasta 1866 MHz.

AMD octal core Zambezi 32 nm SOI.

AMD octal core Zambezi 32 nm SOI.

Según los directivos de marketing de AMD en declaraciones del día 8 de Agosto, clock for clock y core for core, Bulldozer superará a Phenom II (45 nm) en un 10% en IPC.

En proceso single thread aseguran que la diferencia será mayor gracias a modos Turbo mucho más optimizados (más frecuencia con menor voltaje).

Y el rendimiento por socket aumentará más notablemente gracias a:

- Un 33 % más de cores por socket (8 vs. 6 cores)

- Un 10 % más de velocidad por core y por clock.

Esperan mejoras del 50% sobre un AMD Thuban hexacore a la misma frecuencia en proceso multithread de saturación (100% de carga).

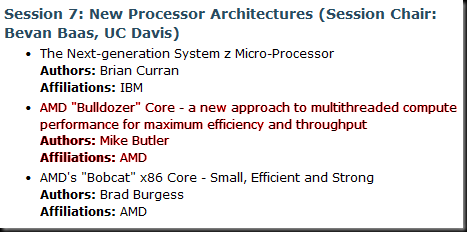

Por último puntualizar que el 24 de este mes AMD hará pública la microarquitectura Bulldozer con motivo del Hot Chips 22.

De 5:00 a 6:30 h por fin conoceremos los nuevos Bulldozer.

De 5:00 a 6:30 h por fin conoceremos los nuevos Bulldozer.

También ese mismo día se hablará de los nuevos cores Bobcat de bajo consumo. Os mantendré informados de todos los detalles.

El conjunto AMD-ATI está evolucionando muy positivamente, espero que siga así, buen artículo,

ResponderEliminarUn saludo Carlos!!

Juan Fran,

ResponderEliminarTienes razón, AMD está mostrando una evolución favorable desde que Dirk Meyer se hiciera cargo de la compañía.

Esperemos que en 2011 pueda cumplir sus ambiciosos roadmap y ejecutar sus tres nuevos proyectos en 32 nm:

- Para la gama más alta Bulldozer.

- La APU Llano para el mercado general basada en cores Phenom II evolucionados.

- Bobcat, el rival de Atom.

Por cierto, estoy de vacaciones la primera y segunda semana de Agosto. Hoy estoy en TGN, ayer estuvimos en el acuario de BCN y ahora vamos para La Pineda a pasar la semana ya que la siguiente trabajo de nuevo...

Un saludo,

Carlos Yus.

Que bién Carlos!! jeje pues a disfrutar las vacaciones, siempre que hablo contigo estas de vacaciones!!! que bién vives! jeje, pues algún día que tengas libre haber si podríamos quedar que yo comienzo vacaciones la semana que viene, 2 semanas, un saludo!!

ResponderEliminarEL POSIBLE RENDIMIENDO DE BULLDOZER LO CALCULASTE MAL, BULLDOZER PODRÁ EJECUTAR 4 IPC (LOS PHENOM SOLO 3 IPC) , TENDRÁ UNA PIPELINE MÁS CORTA QUE LOS PHENOM Y NUEVAS INSTRUCCIONES Y CONTROLADOR DE MEMORIA. A SIMPLE VISTA UN CORE BULLDOZER ES 30 A 35 % MÁS RAPIDO QUE LOS PHENOM EN TAREAS MONOHILO. CUANDO SE TRABAJE EN MULTIHILO AL TENER PARTES COMPARTIDAS ENTRE CORES SE PERDERA UN 10% DE RENDIMIENTO BRUTO.

ResponderEliminarAnónimo,

ResponderEliminarBulldozer, por INT core ejecutará un pico máximo de dos operaciones ALU y 4 por cada conjunto de dos INT cores, el llamado módulo. Un Bulldozer octa-core tendrá un pico máximo teórico de 16 INT IPC por chip.

Los Athlon o Phenom en todas sus variantes ejecutan en pico 3 IPC en enteros por core. Un Phenom II X6, por ejemplo, da un pico de 18 INT IPC en pico por chip.

El pipeline de Bulldozer será considerablemente más largo que el de Phenom II, obviamente. Yo apuesto por un mínimo de 18 etapas en enteros.

Un saludo,

Carlos Yus